Signal Integrity (SI) in PCB design is the practice of ensuring signals are transmitted cleanly and without distortion from the driver to the receiver. Achieving good signal integrity involves managing a layout to control impedance, minimize reflections, reduce crosstalk, and maintain a stable power delivery network. As clock speeds increase and voltage levels drop, a proactive approach to SI is no longer optional but a critical requirement for a functional and reliable electronic product. This guide compares different layout strategies to help you make informed decisions that prevent costly board respins.

Table of Contents

- The Four Horsemen of SI Degradation: Understanding the Core Problems

- The Foundation: Comparing PCB Stack-up Strategies

- Strategic Trace Routing: A Comparative Analysis

- Choosing the Right Termination Strategy

- Component Placement and Power Integrity (PI)

- Putting It All Together: A Holistic Approach

- Frequently Asked Questions (FAQ)

The Four Horsemen of SI Degradation: Understanding the Core Problems

Before comparing layout solutions, it’s essential to understand the problems they aim to solve. Most signal integrity issues fall into four main categories. Ignoring these fundamental challenges can lead to intermittent failures, data corruption, and a non-functional design, regardless of how well-chosen your components are.

Reflections and Impedance Mismatches

At high frequencies, a PCB trace behaves like a transmission line with a characteristic impedance. When a signal traveling down this trace encounters a change in impedance—at a connector, a via, a component pin, or the end of the line—a portion of the signal’s energy is reflected back towards the source. This reflected energy can combine with the original signal, causing distortion, overshoot (voltage exceeding the rail), and undershoot (voltage dropping below ground). Severe reflections can cause false logic triggering and corrupt data transmission, making impedance matching one of the most critical aspects of SI.

Crosstalk (Signal Coupling)

Crosstalk, or signal coupling, occurs when the electromagnetic field from one trace (the “aggressor”) induces an unwanted signal in an adjacent trace (the “victim”). This is a form of noise that can degrade the victim signal’s quality, reduce noise margins, and even cause it to switch states incorrectly. The amount of crosstalk depends on several factors, including the distance between traces, the length over which they run parallel, the signal rise time, and the height of the traces above the reference plane. As board densities increase, managing trace spacing to mitigate crosstalk becomes a significant layout challenge.

Power and Ground Noise

A stable power delivery network (PDN) is the bedrock of good signal integrity. Two common issues are ground bounce and power ripple. Ground bounce happens when multiple outputs switch simultaneously, causing a rapid change in current flow through the package’s lead inductance. This results in a temporary voltage shift on the “ground” pin, which is no longer a stable 0V reference. This noise can propagate to other components, disrupting their operation. A robust PDN, designed with power and ground planes and sufficient decoupling, is essential to provide a low-impedance path for return currents and suppress this noise.

EMI (Electromagnetic Interference)

A PCB that radiates excessive electromagnetic energy is not just a signal integrity problem; it’s a compliance failure. Loops formed by signals and their return paths act as antennas, radiating EMI. Likewise, a poorly designed board can be susceptible to external EMI. Good SI practices, such as maintaining a continuous ground plane, using differential signaling, and minimizing loop areas, are also fundamental EMI mitigation techniques. A board designed with SI in mind is inherently quieter and more robust against external interference.

The Foundation: Comparing PCB Stack-up Strategies

Your PCB layer stack-up is the first and most impactful decision you will make for signal integrity. It defines the impedance of your traces, the effectiveness of your shielding, and the quality of your power delivery network. Two primary trace configurations dominate modern PCB design: microstrip and stripline.

Microstrip vs. Stripline: Which Configuration is Right for Your Design?

The choice between microstrip and stripline routing is a trade-off between cost, performance, and routing density. A microstrip trace is routed on an outer layer of the PCB, with a single reference plane (usually ground) beneath it. A stripline trace is routed on an internal layer, sandwiched between two reference planes.

Microstrip is generally cheaper to fabricate and easier to route and inspect. However, because one side is exposed to air (which has a different dielectric constant than the PCB material), its electromagnetic fields are not fully contained. This makes it more susceptible to generating EMI and being affected by crosstalk. In contrast, stripline offers superior performance. The two reference planes fully contain the electromagnetic fields, providing excellent shielding, tighter impedance control, and significantly lower crosstalk and EMI emissions. The downside is higher fabrication cost and more complex routing, as the traces are buried within the board.

| Feature | Microstrip | Stripline |

|---|---|---|

| Layer Location | Outer layer (e.g., Top, Bottom) | Inner layer |

| Reference Planes | One | Two (above and below) |

| Impedance Control | Good | Excellent |

| EMI/EMC Performance | Fair (unshielded) | Excellent (shielded) |

| Fabrication Cost | Lower | Higher |

| Propagation Speed | Faster (mixed dielectric of air and substrate) | Slower (uniform dielectric of substrate) |

| Best For | Cost-sensitive designs, non-critical signals, lower-speed interfaces. | High-speed signals (e.g., PCIe, DDR), critical clocks, noise-sensitive applications. |

The Critical Role of a Solid Ground Plane

Regardless of your chosen configuration, the most important element of any stack-up is a solid, uninterrupted ground plane. This plane serves two critical functions. First, it acts as the reference for controlled impedance traces. Any split or gap in this plane under a high-speed trace creates a significant impedance discontinuity, causing severe signal reflections. Second, it provides the lowest inductance return path for signals. High-frequency signals want to return directly underneath their forward path. A solid ground plane facilitates this, minimizing the loop area and drastically reducing EMI radiation. Never route a high-speed signal over a split in the ground plane.

Strategic Trace Routing: A Comparative Analysis

Once the stack-up is defined, the focus shifts to how traces are routed. The physical path a signal takes has a direct impact on its quality, timing, and susceptibility to noise.

Impedance Control: The Non-Negotiable Rule

As discussed, maintaining a consistent characteristic impedance is paramount. This is achieved by carefully controlling the trace width, its height above the reference plane (dielectric thickness), and the dielectric constant of the material. Any deviation from the target impedance (e.g., 50 ohms for single-ended, 100 ohms for differential) will cause reflections. EDA tools include impedance calculators to determine the correct trace geometry based on your stack-up. This is not a “strategy” to be compared, but a fundamental requirement for all high-speed signals.

Routing Topologies: Daisy-Chain vs. Star vs. Fly-by

When a single driver needs to connect to multiple receivers, the routing topology matters. A star topology routes separate traces from the driver to each receiver. This provides excellent signal quality to each receiver but can be difficult to route and can cause timing skew issues since the trace lengths are often different. A daisy-chain topology routes from the driver to the first receiver, then to the second, and so on. This is easier to route but creates stubs at each receiver tap, which can cause significant reflections. It requires careful termination at the end of the line.

Modern memory interfaces like DDR3/4/5 often use a fly-by topology. This is a variation of the daisy-chain where the main bus trace runs past the receivers, and very short stubs branch off to connect to each component. This minimizes the stub effect and improves signal integrity at very high data rates, combined with on-die termination (ODT) within the memory chips themselves.

Managing Differential Pairs for Superior Noise Immunity

Differential signaling uses two complementary traces (+ and -) to transmit a single signal. The receiver looks at the voltage *difference* between the two lines, not their absolute voltage relative to ground. This provides excellent common-mode noise rejection, as any noise (like crosstalk or ground bounce) picked up by the pair will affect both traces equally and be ignored by the receiver. For this to work effectively, the two traces must be tightly coupled:

- Length Matching: The two traces must be kept as close to the same length as possible to ensure the signals arrive at the receiver simultaneously.

- Symmetry: The routing should be symmetrical, and any discontinuities (like vias) should be applied to both traces identically.

- Spacing: The spacing between the traces should be kept constant to maintain a consistent differential impedance (e.g., 100 ohms).

Bends, Vias, and Stubs: The Devil is in the Details

Even small geometric features can degrade signals. While the old rule of “never use 90-degree bends” is less critical with modern fabrication, it’s still best practice to use 45-degree bends or curved traces to avoid sharp impedance changes. Vias are a major source of discontinuity. They introduce capacitance and inductance, and the unused portion of a via barrel (a “via stub”) can create a resonant structure that annihilates signal quality at specific frequencies. For very high-speed designs (e.g., >10 Gbps), techniques like back-drilling are used to remove the unused stub. Any unterminated trace branching off the main signal path is a stub and should be avoided or kept extremely short.

Choosing the Right Termination Strategy

Termination is the practice of adding a resistor to a transmission line to match its impedance, thereby absorbing the signal’s energy at the end of the line and preventing reflections.

When to Terminate: A Guideline

Not every trace needs termination. A common rule of thumb is that a trace needs to be treated as a transmission line and terminated if its length is greater than 1/6th of the signal’s wavelength during its rise time. In simpler terms, if the time it takes for the signal to travel down the trace and back is a significant fraction of its rise time, reflections become a problem. For modern high-speed signals with sub-nanosecond rise times, this means almost all but the very shortest traces require termination.

Comparing Termination Schemes: Series, Parallel, Thevenin, and AC

Choosing the right termination scheme involves trade-offs between component count, power consumption, and effectiveness.

- Series Termination: A resistor is placed near the driver. It’s simple and consumes no DC power, but it slows down the signal’s rise time, which can sometimes be a benefit.

- Parallel Termination: A resistor is placed at the receiver, connecting the trace to VCC or GND. It’s very effective at terminating the line but constantly draws DC power when the line is held high (if terminated to GND) or low (if terminated to VCC).

- Thevenin Termination: Uses a voltage divider (two resistors) at the receiver, connecting to both VCC and GND. It provides an excellent impedance match but consumes significant DC power regardless of the signal state.

- AC Termination: A resistor and capacitor are placed in series at the receiver. It provides termination for the high-frequency components of the signal without any DC power consumption, but it adds complexity and component count.

| Termination Scheme | Location | Pros | Cons |

|---|---|---|---|

| Series | Near Driver | Simple, zero DC power consumption, can slow edge rates. | Not suitable for multi-receiver (bused) topologies. |

| Parallel | Near Receiver | Excellent termination, works for bus topologies. | Consumes DC power when signal is in one state. |

| Thevenin | Near Receiver | Excellent termination, provides a defined DC bias. | Consumes significant DC power in both signal states. |

| AC | Near Receiver | Good termination, zero DC power consumption. | Adds capacitor, can distort low-frequency signals/duty cycles. |

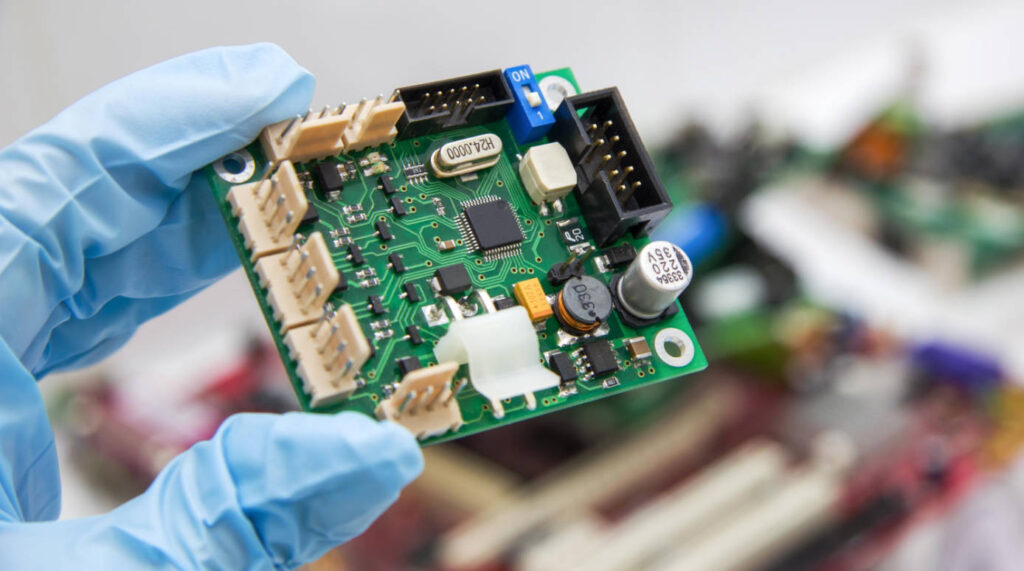

Component Placement and Power Integrity (PI)

Signal Integrity and Power Integrity (PI) are two sides of the same coin. A noisy power rail can easily corrupt a perfectly routed signal. Good component placement and a robust decoupling strategy are essential.

Strategic Component Placement for Shorter Signal Paths

The first step in layout should be a logical floor plan. Place interconnected components close to each other to keep trace lengths short. This is especially true for high-speed interfaces like memory or CPU buses. Shorter traces have less loss, generate less EMI, are less susceptible to crosstalk, and may even eliminate the need for termination in some cases. Prioritize the placement of critical components and their associated circuitry before routing less critical signals.

The Art of Decoupling: Bypass Capacitors Explained

Digital ICs draw current in fast, high-frequency bursts when they switch. The PDN’s inductance can prevent the power supply from delivering this current quickly enough, causing the voltage rail to droop. Decoupling capacitors (or bypass capacitors) act as tiny, local energy reservoirs placed right next to the IC’s power pins. They supply this instantaneous current, keeping the voltage rail stable. A common strategy is to use a range of capacitor values (e.g., 1µF, 0.1µF, 0.01µF) placed as close as possible to the IC power pins. The smallest value capacitors have the lowest inductance and can respond to the fastest current demands, while the larger capacitors handle lower-frequency needs.

Putting It All Together: A Holistic Approach

Effective signal integrity design is not about applying a single rule but about adopting a holistic methodology. It begins with a smart layer stack-up, moves to a strategic floor plan, and continues with meticulous routing and termination. Each strategy—from choosing stripline over microstrip for a critical clock to placing a 0.01µF capacitor right at a power pin—is a piece of a larger puzzle. The best strategy is always a balanced one, making intelligent trade-offs between performance, cost, and manufacturability based on the specific requirements of your design.

Frequently Asked Questions (FAQ)

What is the 3W rule in PCB design?

The 3W rule is a guideline to minimize crosstalk. It states that the center-to-center distance between two adjacent traces should be at least three times the width (W) of a single trace. For more critical signals, a 10W rule is sometimes used. While it’s a good starting point, its effectiveness depends on the trace height above the ground plane, and modern SI simulation tools provide more accurate analysis.

How do I length match traces in my PCB layout software?

Most professional EDA tools (like Altium Designer, Cadence Allegro, or KiCad) have features for length matching. You define a “matched length” constraint for a group of signals (a net class), and the software allows you to add serpentine or “accordion” sections to the shorter traces to increase their length until they match the longest trace within a specified tolerance.

Why should I avoid routing high-speed signals over a split plane?

When a high-speed signal crosses a split in its reference plane, its return current cannot flow directly beneath it. It must find an alternate, longer path around the split. This dramatically increases the size of the current loop, which acts as an efficient antenna, radiating significant EMI. It also creates a massive impedance discontinuity, causing severe signal reflections that can render the signal unusable.

Signal Integrity, PCB Design, PCB Layout, High-Speed Design, signal integrity pcb design strategies, how to improve signal integrity in pcb, pcb layout techniques for high-speed signals, comparing microstrip and stripline, crosstalk reduction techniques pcb, impedance control in pcb layout, termination strategies for signal integrity, differential pair routing, ground plane design, power integrity